CZECH TECHNICAL UNIVERSITY Faculty of Electrical Engineering Department of Electromagnetic Field

# **Evolutionary Design of Microwave Circuits** Diploma Thesis

Tomáš Müller

Supervisor: Prof. Ing. Zbyněk Škvor, CSc.

May 2003

# Acknowledgements

Many thanks to Prof. Ing. Zbyněk Škvor, CSc. for patient and systematic guidance in creation of this diploma thesis.

Prohlašuji, že jsem svou diplomovou práci napsal samostatně a výhradně s použitím citovaných pramenů. Souhlasím se zapůjčováním práce.

I claim that I have developed this diploma thesis individually and exclusively with the use of the cited sources. I agree with lending of this work.

Prague, 23<sup>rd</sup> May, 2003

Tomáš Müller

# **Table of Contents**

| <u>0</u> . | INT           | <u>TRODUCTION</u>                                                    | .1 |

|------------|---------------|----------------------------------------------------------------------|----|

| 1.         | EV            | OLUTION                                                              | .2 |

|            | 1.1.          | Genetic Algorithms                                                   | .2 |

|            | 1.2.          | Evolutionary (single individual population, local search) algorithms | .4 |

|            |               | Hill-Climbing                                                        |    |

|            | 1.2.2.        | Hill-Climbing-Random-Walk                                            | .6 |

|            |               | Tabu-Search                                                          |    |

|            | 1.2.4.        | Simulated-Anealing                                                   | .7 |

|            | 1.2.5.        | Stochastic Hill-Climbing                                             | .8 |

|            | 1.2.6.        | Local Search                                                         | .9 |

|            | 1.3.          | Conclusion                                                           | .9 |

| <u>2</u> . | TH            | E ALGORITHM PROPOSAL 1                                               | 0  |

|            | <u>2.1.</u>   | Algorithm Requirements 1                                             | 0  |

|            | <u>2.2.</u>   | Circuit Representation                                               | 0  |

|            | <u>2.3.</u>   | Evaluation of Circuits                                               | 12 |

|            | 2.4.          | Circuit's Neighbourhood                                              | 4  |

|            | <u>2.5.</u>   | Initial Configuration                                                |    |

|            | <u>2.6.</u>   | Algorithm                                                            | 17 |

|            | 2.6.1.        | Operation Selection                                                  | 8  |

|            | 2.6.2.        | Acceptance Criterion                                                 | 9  |

|            | <u>2.7.</u>   | Algorithm Improvements                                               | 19 |

|            | 2.7.1.        | Local (Parameter) Optimization                                       | 19 |

|            | <u>2.7.2.</u> | Backtracking                                                         | 20 |

|            | 2.7.3.        | RMS Error Estimation                                                 | 22 |

|            | <u>2.8.</u>   | Conclusion                                                           | 25 |

| <u>3</u> . | IM            | PLEMENTATION ISSUES                                                  | 26 |

|            | 3.1.          | Circuit Elements                                                     | 26 |

|            | 3.2.          | Circuit Representation                                               |    |

|            | 3.3.          | Operations                                                           |    |

|            | 3.4.          | Frequency Requirements                                               | 29 |

|            | 3.5.          | Analysis                                                             | 31 |

|            | 3.6.          | Design                                                               | 32 |

|            | 3.7.          | Conclusion                                                           | 32 |

| 4.         | PRA           | ACTICAL RESULTS                                                      | 34 |

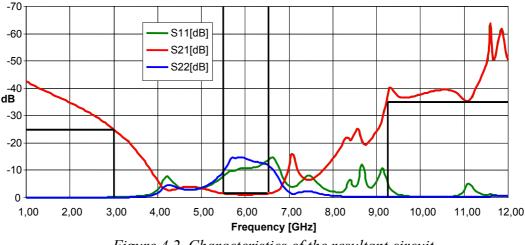

|            | 4.1.          | A Band Pass Filter                                                   | 34 |

|            | 4.1.1.        | First Execution                                                      | 35 |

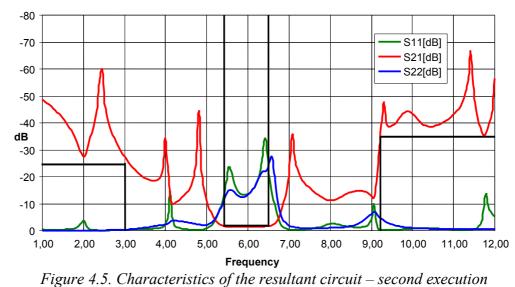

|            | 4.1.2.        | Second Execution.                                                    | 36 |

|            | 4.2.          | An Amplifier                                                         |    |

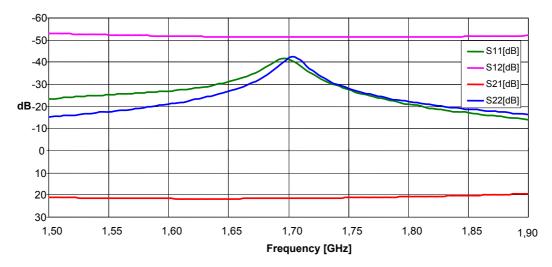

|            |               | First Execution                                                      |    |

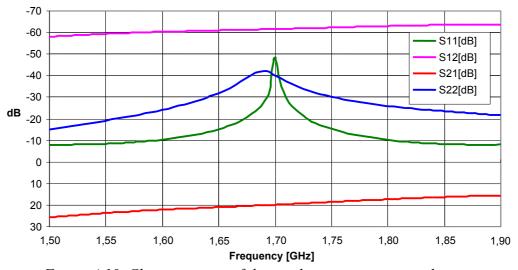

|            |               | Second Execution                                                     |    |

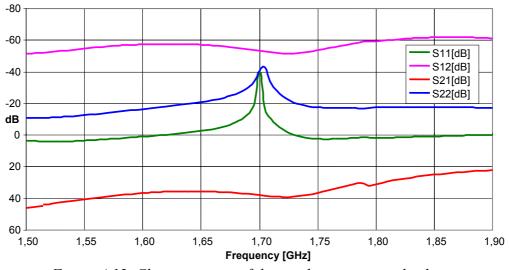

|            |               | Third Execution.                                                     |    |

|            |               |                                                                      |    |

| 4.3. A Frequency Spl        | itter                   | 2 |

|-----------------------------|-------------------------|---|

| 4.4. Conclusion             |                         | 4 |

| 5. <u>CONCLUSION</u>        |                         | 6 |

| <u>6.</u> <u>REFERENCES</u> |                         | 7 |

| APPENDIX A USER D           | OCUMENTATION A-         | 1 |

| A.1. Prerequisites          |                         | 1 |

| A.2. Installation           |                         | 1 |

| <u>A.3.</u> <u>Usage</u>    |                         | 1 |

| A.4. Input File             |                         | 1 |

| A.4.1. Section CONFIC       | JURATION                | 1 |

| A.4.2. Section LINKS        |                         | 4 |

| A.4.3. Section NODES        |                         | 4 |

| A.4.4. Section OPERA        | <u>ΓΙΟΝS</u> Α          | 4 |

| A.4.5. Section OPT          |                         | 6 |

| A.5. Output Files           |                         | 7 |

| APPENDIX B PROGR            | AM EXTENSION EXAMPLES   | 1 |

| B.1. New Circuit Eler       | ment Implementation     | 1 |

| B.2. New Circuit Ope        | ration ImplementationB- | 3 |

| APPENDIX C CD-ROM           | M CONTENTC-             | 1 |

|                             |                         |   |

# 0. Introduction

Evolutionary and genetic algorithms are powerful multi-purpose optimization tools that model the principles of evolution. They are often capable of finding globally optimal solution even in the most complex search spaces.

The mission of this thesis is to propose and implement an evolutionary (single-member population) algorithm for designing microwave circuits. The main goal is to present a possibility of usage of evolutionary algorithms in computer aided design of microwave circuits, not to produce some universal designing product.

The computer aided design of microwave circuits represents tools for design, evaluation and optimization of microwave circuits. Nowadays, optimization in the microwave circuit design means finding circuit element values for a fixed circuit topology, where the circuit topology can be e.g. an input parameter. A different approach is presented in this work: the design of a microwave circuit is left completely to the evolutionary (design and optimization) algorithm. Input parameters include design goals (e.g. required frequency response), number of circuit ports and a set of available circuit elements. The evolutionary algorithm then sets up different circuit topologies, and the topology that satisfies goals is an output parameter, together with circuit element values.

The thesis is organized in several chapters. In the first chapter, the general principles and methods of evolutionary algorithms are described, with the main emphasis on their usage in the circuit design. In the second chapter the algorithm for the design of microwave circuits is proposed. The implementation of the proposed algorithm in Java is outlined in the following third chapter. The fourth chapter contains some practical results achieved with the implemented algorithm on some basic assignments. There are also several appendixes. A user documentation of the implemented program is included in appendix A. In appendix B, some examples of extensions of the implemented algorithm are shown. Finally, appendix C contains an organization structure of the CD-ROM, which is included in the thesis.

# 1. Evolution

Evolutionary (genetic) algorithms are powerful general purpose optimization tools which model the principles of evolution [1, 10, 11]. They are often capable of finding globally optimal solution even in the most complex search spaces. They operate on a population of members which are selected according to their quality and then used as the basis for a new generation of members found by combining (crossover) and/or altering (mutating) current individuals.

### 1.1. Genetic Algorithms

A *genetic algorithm* [10, 11] starts by generating an initial population (a set of initial solution candidates, members). Basically, each member is represented by a set of genes, encoded as a bit string with the fixed length.

The algorithm works in iterations, evolutions of a population. In each evolution step, a new population is produced from the previous one. There are several methods how to produce a new population. Most of them use three different operators:

- selection of two parents (e.g. according to some evaluation of parents)

- crossover of parents (e.g. combining of their genes)

- mutation of the arose individual (e.g. by swapping several genes)

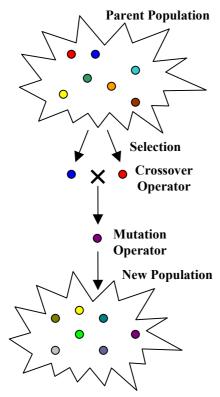

Figure 1.1. An evolution step

An example of a new population creation is presented in Figure 1.1. It starts with an empty generation. Until this new generation has the demanded number of members: Two members are selected (via selection operator) from the parent population and combined (via crossover operator). The resultant individual is then altered (via mutation operator) and placed into the new population.

The algorithm stops when there is a suitable solution found. It means that there is a member in the new population which fits the input requirements. Otherwise, the new population becomes the parent population for a new evolution step.

Another version of the genetic algorithm can for example work with the crossover of two arbitrary (randomly selected) members from the parent population, where only those created individuals that are good enough are placed into the new population. The selection is moved after crossover and mutation operator in this example. Typically, the number of members in a population is constant during the search. However, there are also approaches in which the number of population members differs during the search (e.g. according to their quality) [8].

The selection of the two members from the parent population can be based on the possibility of evaluation of these candidates. Whether it is possible to evaluate each member, which means that there is a mapping function of each member to a number according to its quality. Or whether we can only compare two members and say which of them is better. In the first case, the probability of a selection of a candidate can be guided according to its evaluation. For example:

$$P_a = \frac{eval(a)}{\sum_{s \in M} eval(s)}$$

Figure 1.2. Probability of acceptance according to the evaluation

where a is a member from population M and eval is the evaluation function (a better solution corresponds to a higher number). This approach is called *roulette wheel selection*, see [8] for details. In the second case, where we can only mutually compare two members, the *tournament selection* can be used [8]. In such case, the selection is made in several rounds. In the first round, two members are selected randomly (with uniform probability) and the better one is used for the second round. In each next round, one member is taken randomly and compared to the previous winner (previous better solution). After several rounds, the winner is returned as the selected element. Another possibility of organizing the tournament is based on a binary tree, where in each round, the number of candidates (from the initial randomly selected subset of the population) is divided by two.

Often, the crossover operator is the most crucial step in the design of a genetic algorithm. Traditionally, the search mechanism has been domain independent. That means the crossover and mutation operators have no knowledge of the problem and what a good solution would be. They are working with members represented as binary strings, combining and mutating their genes. For example, the crossover operator can be designed as splitting of the genes into the two parts (e.g. genes at odd or even position in the bit string) and combination these parts from the respective parents (e.g. odd bits from the first parent, even bits from the second, as shown in Figure 1.3). The mutation operator can be than designed as a switch of randomly selected fixed number of genes (e.g. three genes are swapped in Figure 1.4).

10011111011101 010111101011011 1101111010011001 Figure 1.3. Crossover operator example

<u>110111110110011001</u> <u>110101110100011101</u> *Figure 1.4. Mutation operator example*  The disadvantage of this approach is that the given solution (e.g. circuit represented by the bit string) is often much different from both parent solutions. In many cases [8, 11], it was empirically shown that the use of domain dependent operators is much more efficient in practice. Such operators are trying to obtain a solution which is better than both its parent solutions, e.g. a solution which takes the best "features" from both parents. In some literature [2], such algorithms are called memetic algorithms, because they are working with bigger entities than genes (called memes).

#### 1.2. Evolutionary (single individual population, local search) algorithms

Because of the computational demands and high complicatedness of design of crossover operator for the microwave circuits (members of a population), we will focus on (in some sense extreme) case of the genetic algorithm, where the population has always cardinality equal to one. In each evolution step, the algorithm takes the previous (parent) solution and by its mutation it creates other (children) solutions from it. Finally, one of the generated solutions is picked up to be the parent for the next iteration step.

There are naming differences: Such algorithms are sometimes called evolutionary (to distinguish them from genetic algorithms, which work with bigger population). But sometimes, the expression evolutionary algorithm is used for the class of all algorithms, which mimics the process of evolution (genetic algorithms belong to this class of evolutionary algorithms).

This single-member population approach can also be considered as a variation of the local search algorithms. These algorithms also work in iterations, with one infeasible solution. In each iteration step, neighbour solutions from the previous solution are generated and evaluated. At the end of the iteration, one neighbour solution is selected into the next iteration. The purpose of these algorithms is simple: They are repeatedly trying either to decrease the number of inconsistencies in the solution and/or to get closer and closer to some optimal one.

Recently, there have been developed many kinds of the local (neighbour) search algorithms (e.g. hill climbing, steepest descant, min-conflict, genet) and their improvements (e.g. random walk, tabu-list, simulated annealing). We will discuss some of these algorithms in the following subsections.

Genetic algorithms with a single member population and local search algorithms work in iterations, always with one configuration (or state, solution, solution candidate). In the design of microwave circuits, such configuration will be a microwave circuit (both with topology and values of all circuit elements). Each such solution should have an evaluation value and a set of neighbour solutions defined. For us, value of a circuit can express its difference from the required, searching solution. The neighbour solutions can be defined as a circuits derived from the previous one by applying a mutation operator. Such mutation can be for example a change of a single circuit element, or some circuit value or a simple change of circuit topology.

# 1.2.1. Hill-Climbing

*Hill-climbing* (or *steepest-descendant*) is probably the most famous algorithm of local search [7, 8]. The idea of hill-climbing is following:

- 1. start at randomly generated configuration

- 2. move to the neighbour with the best evaluation value

- 3. if a strict local-minimum is reached (there is no better neighbour) then restart at another randomly generated configuration

- 4. if sufficient (required) configuration is found then return solution

- 5. otherwise repeat to step 2

The hill-climbing procedure repeats local steps to neighbourhood till the solution is found or the time exceeds the limit for the computation. Visibly, the algorithm does not guarantee to find the best solution but it can return any "solution" at each time (the longer time, the better solution). Therefore, this algorithm (and all other algorithms in this section) belongs to the group of *anytime algorithms* that are able to return some "reasonable" solution at each time. The name of the algorithm, hill-climbing, is derived from its original principle when a maximum was searched by climbing – increasing the evaluation value (note, that are descending now because of looking for the minimum).

In the algorithm presented in Figure 1.5, the parameter *max\_flips* is used to limit the maximal number of moves between restarts which helps to leave non-strict local minimum. The resultant solution has to have the evaluated value below the *limit*.

```

procedure HC(max_moves, limit)

restart: s <- random initial configuration;

for j:=1 to max_moves do

if eval(s)<=limit then return s;

if s is a strict local minimum then

go to restart;

else

s <- neighbour with smallest evaluation value;

end if

end for

go to restart;

end HC</pre>

```

Figure 1.5. Hill Climbing algorithm

Remark that the hill-climbing algorithm has to explore all neighbours of the current state before choosing the move. In general, this can take a lot of time. To avoid exploring all neighbours of the current configuration some alternatives were proposed to find the next move.

For example, randomized hill-climbing are repeatedly choosing the neighbour randomly, until a better neighbour than the current solution is found. This neighbour is choosen for the following iteration.

Another approach is to select neighbours according to some heuristics, some ordering of neighbours according to their quality. Again, until the first better neighbour than the current state is found.

### 1.2.2. Hill-Climbing-Random-Walk

Because the pure hill-climbing algorithm cannot go beyond a local-minimum, some noise strategies were introduced here. Among them, the *random-walk* strategy becomes one of the most popular [6]. For a given configuration, the random-walk strategy picks randomly a neighbour with probability p, and apply the hill-climbing strategy (e.g. selection of the best neighbour) with probability 1-p. See Figure 1.6.

```

procedure HCRW(max_moves, limit, p)

s <- random initial configuration;

nb_moves <- 0;

while eval(s)>limit & nb_moves<max_moves do

if probability p verified then

s <- randomly choosen neighbour;

else

s <- neighbour with smallest evaluation value;

end if

nb_moves <- nb_moves + 1;

end while

return s;

end HCRW</pre>

```

Figure 1.6. Hill Climbing Random Walk algorithm

This algorithm is controlled by the random probability p, it should be clear that the value for this parameter has a big influence on the performance of the algorithm. The preliminary studies determined the following feasible ranges of parameter values  $0.02 \le p \le 0.1$ .

# 1.2.3. Tabu-Search

Tabu search [3, 8] is another method to avoid cycling and getting trapped in local minimum. It is based on the notion of tabu list, that is a special short term memory that maintains a selective history, composed of previously encountered configurations or more generally pertinent attributes of such configurations (the change of the configuration, e.g. a pair <circuit\_element, circuit\_value> when there is only moves changing a value of an arbitrary circuit element – no topology changes). A simple TS strategy consist in preventing configurations of tabu list from being recognised for the next k iterations (k, called tabu tenure, is the size of tabu list). Such a strategy prevents Tabu from being trapped in short term cycling and allows the search process to go beyond local optima.

Tabu restrictions may be overridden under certain conditions, called *aspiration criteria*. Aspiration criteria define rules that govern whether next configuration is considered as a possible move even it is tabu. One widely used aspiration criterion consists of removing a tabu classification from a move when the move leads to a solution better than that obtained so far. See Figure 1.7.

Again, the performance of Tabu Search is greatly influenced by the size of tabu list *tl*. A preliminary studies determined the following feasible range of parameter values  $10 \le tl \le 35$ .

```

procedure TS(max_moves, limit)

s <- random initial configuration;

nb_moves <- 0;

initialise randomly the tabu list;

while eval(s)>limit & nb_moves<max_moves do

choose a move, e.g. <element, value> with the best

performance among the non-tabu moves and the moves

satisfying the aspiration criteria;

introduce the move, e.g. <element, value> in the tabu list;

remove the oldest move from the tabu list;

apply the move to the s;

nb_moves <- nb_moves+1;

end while

return s;

end TS</pre>

```

Figure 1.7. Tabu Search algorithm

# 1.2.4. Simulated-Anealing

Another meta-heuristic method allowing escape from a local minimum is called *simulated annealing* [5, 8]. The algorithm is derived from the physical process of cooling of a metal in a thermal bath. Quality of the output material is reached so, that the material is alternately heated and cooled.

Similarly to the algorithms described above, this algorithm gradually goes from one configuration to another by repeatedly selecting one of the neighbour configuration randomly. If the solution has lower evaluation value, it is automatically chosen to the next iteration. But, if the randomly selected neighbour has higher evaluation value, if has also a chance to be chosen, according to the following probability

$$p = e^{eval(s) - eval(s')/2}$$

# Figure 1.8. Probability of acceptance for simulated annealing

where s is the previous solution, s' is the randomly selected neighbour solution and T denotes the actual temperature. The algorithm is gradually changing this temperature according to some cooling schedule, which is a part of the algorithm's configuration. While the temperature is decreasing, the probability of choosing the worse neighbour is decreasing as well. So, the whole process is based on the selection of the cooling schedule. This schedule can be also chosen for a particular problem during the execution, e.g. to avoid premature cool down. The algorithm is shown in Figure 1.9.

```

procedure SA(max_moves, limit)

s <- random initial configuration;

for j:=1 to max_moves do

if eval(s)<=limit then return s;

s' <- random neighbour of s;

if (eval(s')>eval(s)) or

(random(0,1)<exp[(eval(s)-eval(s'))/T]) then s=s';

T = g(T,j);

end for

return s;

end SA</pre>

```

Figure 1.9. Simulated Annealing

### 1.2.5. Stochastic Hill-Climbing

Similar algorithm to the simulated annealing is the algorithm called *stochastic hill-climbing* (sometimes also called simulated-annealing) [8]. The main difference is, that every randomly selected neighbour (even better) is selected according to some probability. The traditional probability of acceptance of a neighbour solution is

$$p = \frac{1}{1 + e^{eval(s') - eval(s)/T}}$$

Figure 1.10. Probability of acceptance for stochastic hill climbing

again, where s is the previous (parent) solution, s' is the randomly selected neighbour and T is the current temperature. Function *eval* denotes the solution's evaluated value. See the following Figure 1.11.

```

procedure SHC(max_moves, limit)

s <- random initial configuration;

for j:=1 to max_moves do

if eval(s)<=limit then return s;

s`<- random neighbour of s;

if (random(0,1)<1/(1+exp[(eval(s')-eval(s))/T]))

then s=s';

T = g(T,j);

end for

return s;

end SHC</pre>

```

Figure 1.11. Stochastic Hill-Climbing

The following example table (Figure 1.12.) shows the probability of acceptance for the better neighbour solution (the difference of evaluated values is equal to -13) according to the chosen temperature T. At the beginning, when the temperature is high, the probability of acceptance goes to one half. During the search, while the temperature is decreased, the probability of acceptance of a better neighbour solution goes near to one.

| Т     | $e^{-13/T}$ | Р     |

|-------|-------------|-------|

| 1     | 2e-7        | 1.00  |

| 5     | 0.0743      | 0.93  |

| 10    | 0.2725      | 0.78  |

| 20    | 0.52        | 0.66  |

| 50    | 0.77        | 0.56  |

| 10e10 | 0.9999      | 0.500 |

*Figure 1.12. Probability of acceptance a solution for eval(s')-eval(s) equals to -13 according to temperature T*

The limit case is, when the temperature limitary goes to zero, the better neighbour solution is always accepted (probability goes to one) and the worse neighbour solution is always declined (probability goes to zero).

### 1.2.6. Local Search

All above algorithms are based on common idea known under the notion *local search* [8]. In local search, an initial configuration is generated and the algorithm moves from the current configuration to neighbourhood configurations until a solution (decision problems) or a good solution (optimization problems) has been found or the resources available are exhausted. This idea is expressed in the following general local search algorithm that enables implementation of many particular local search algorithms via definitions of specific procedures, see Figure 1.13.

```

procedure LS(max_tries, max_moves, limit)

s <- random initial configuration;

for i:=1 to max_tries while Gcondition do

for j:=1 to max_moves while Lcondition do

if eval(s)<=limit then return s;

select n in neighbourhood(s);

if acceptable(n) then s<-n;

end for

s <- restartState(s);

end for

return s;

end LS</pre>

```

Figure 1.13. Local Search algorithm scheme

# 1.3. Conclusion

In this chapter, various basic approaches which mimic an evolution of a single individual have been described. In the following chapter, we will propose an evolutionary algorithm for design of microwave circuits on the basis of this knowledge.

Remark that not all of the above presented methods are suitable for an evolution of a single circuit. For example, it is either impossible or at least not effective to evaluate all the neighbours of a circuit, because of the non-discrete character of circuit elements' values. For the same reason (large or infinity cardinality of the circuit's neighbourhood), the tabu-list technique will be also inefficient – a local optimum can also have excessively large neighbourhood.

# 2. The Algorithm Proposal

In this chapter, we will at first summarize the requirements for the evolutionary design algorithm. Next, we will discuss the representation of a circuit, which will be our individual configuration during the evolutionary search. Then, we will propose an evaluation of circuits and we will define the circuit's neighbourhood. Finally, we will describe an evolutionary algorithm handling our requirements and propose several improvements to it.

# 2.1. Algorithm Requirements

As the input, we have the requirements for the wanted microwave circuit, namely:

- the number of circuit ports,

- design goals, e.g. frequency response or in more general any requirements derivable for the S-parameters over the given finite set of frequencies,

- a set of available circuit elements

The goal of the algorithm is to find out a circuit, which will meet the above mentioned requirements. Output of the algorithm should be a structure of the resultant circuit (topology) and values of all used circuit elements. We will discuss some other requirements (e.g. planarity of the resultant circuit) later.

As prerequisites, we can assume that we have a  $(3^{rd} party)$  tool, which can provide us an analysis for the given circuit. In the algorithm implementation, the program MIDE [9] is used (possibility of use program MIDE was a part of the assignment of this work). This program can calculate the S-parameters for the given circuit on the given frequency or on finite set of frequencies. But, this tool also makes some demands on the algorithm, namely:

- We has to use circuit elements compatible (known by) the analysis tool.

- Our circuit representation has to be same or easily transformable to the representation understandable by the analysis tool (this structure is called *net-list* in MIDE, see [9] for details).

- The analysis tool has to provide us some API, so we can repeatedly use it (with no user interaction required).

- There can be some limitation of the size of the circuit demanded by the analysis tool.

# 2.2. Circuit Representation

There are several demands on the representation of a microwave circuit, which we will use. At first, the circuit representation has to be able describe an arbitrary circuit (its topology, circuit elements and values of their parameters) we can obtain during the design process. Next, we has to be able to define a set of neighbour circuit to the given circuit representation and also enumerate representations from this neighbourhood. And finally, the representation has to be convertible to the representation required by the analysis tool.

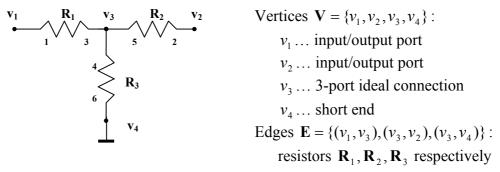

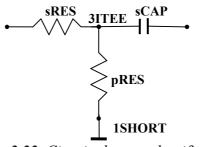

Therefore, the circuit is represented as a graph  $\mathbf{G} = (\mathbf{V}, \mathbf{E})$ , with vertices  $\mathbf{V} = \{v_1, v_2, \dots v_n\}$  and edges  $\mathbf{E} = \{e_1, e_2, \dots e_m\} \subseteq \mathbf{V}^2$  between these vertices. Every edge represents an element (resistor, capacitor, inductor, micro-stripe line, ...), every vertex represents an input/output gate, a connection between one to four elements (ideal or non-ideal) or an element with one or more than two ports (e.g. short end, open end, bounded wiring, ...). The conversion between this representation and the net-list used by program MIDE is straightforward. An example is shown in the following figures:

Figure 2.1. Circuit representation

| BLO circuit 1 2      |                          |

|----------------------|--------------------------|

| RES 1 3 R=R1         | edge (v1,v3) resistor R1 |

| ITEE 3 4 5           | vertex v3                |

| <b>RES 4 6 R</b> =R3 | edge (v3,v4) resistor R3 |

| SHORT 6              | vertex v4                |

| <b>RES 5 2 R</b> =R2 | edge (v3,v2) resistor R2 |

| END                  |                          |

Figure 2.2. Respective net-list for the circuit from Figure 2.1

For ability of a direct connections of two elements represented by vertices (e.g. Figure 2.1. without resistor  $\mathbf{R}_3$  - short end connected directly to vertex  $v_3$ ), there is not strictly required for an edge to have assigned a circuit element. In the implementation, such edge has assigned a special element called *zero element*. Such edges are not included in the resultant net-list structure. Zero elements are also used for vertices with ideal connection of two edges.

So, the above described representation of a circuit gives us a possibility to represent an arbitrary circuit and it is easy transformable to the net-list representation (implemented by simple listing of all edges and vertices, where each edge have assigned two unique numbers, one for each end). Representation of a circuit as a graph gives us also a huge possibility to define several kinds of its neighbours, e.g. by simple graph operations, for example by adding an edge or splitting an edge into two edges connected with a new vertex.

Remark that according to the net-list structure, input and output ports can be connected exactly to one circuit element and each port (denoted by its number) can be shared by exactly two different circuit elements – it has to occur in the net-list exactly twice. There are special elements for connection of more than two ports (e.g. ITEE for ideal connection of three ports – see Figure 2.1 and 2.2). This behaviour has to be propagated into the representation, namely:

- Input/output vertices can have only one edge.

- Each inner vertex can contain at least one and at most four edges (because there is no connection element for more than four ports in MIDE).

- Graph has to be connected. It means, that there has to exist a path between each two different vertices in the graph.

- Each vertex and edge has to have an appropriate circuit element associated. And such element has to have the correct number of ports (two for the edge, number of edges connected to vertex for the vertex). There are two special elements: An element denoting that the vertex is an input/output port (appropriate number of such elements has to be used). A zero element as described above.

- Each circuit element has to have appropriate parameters assigned: In dependence of the type of an element, it can contain zero, one or more parameters with assigned values of respective type and from respective bounded domain (interval). For example, a resistor contains one parameter, its resistance (measured in ohms) from the interval of values <0.001;155555>. There is also an implicit value defined, e.g. for the resistor it is 50 ohms.

# 2.3. Evaluation of Circuits

As it is mentioned above, the external analysis tool MIDE is used for the evaluation of a circuit on the given frequency or on the given finite set of frequencies. Such evaluation gives us a square matrix of S-parameters for each frequency, which represents S-parameters between each pair of input/output ports. From such evaluation we would like to compute one real number denoting the quality (or closeness) of the circuit to the input requirements. Resultant function is called *objective function*.

At first, the set of frequencies, which will be used in analysis can be derived from the requirements. Remark, that our requirements are defined as requirements derivable from S-parameters (e.g. frequency response) on the given finite set of frequencies. For example, we can require the transmission of a filter between 1GHz and 3GHz step 100MHz (it means on frequency 1GHz, 1.1GHz, 1.2GHz, ... 3GHz) to be below -25dB.

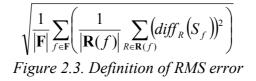

So, we have requirements on the given frequencies and computed characteristics for the given circuit. Than we can compute the root mean square (RMS) error from differences between these results and requirements, as follows:

where  $\mathbf{F} = \{f_1, f_2, \dots f_n\}$  is a finite set of given frequencies,  $\mathbf{R}(f)$  denotes the set of requirements on the given frequency,  $S_f$  are the computed S-parameters for the frequency f and  $diff_R(S_f)$  denotes the difference between the computed Sparameters  $S_f$  and the requirements R, so that the difference is zero, if the requirement is met. For example, in case of a requirement expressed as an inequality, e.g. transmission to be below -25dB, the difference is zero if the transmission is bellow the given limit. Otherwise it expresses the difference of required and measured transmission in decibels.

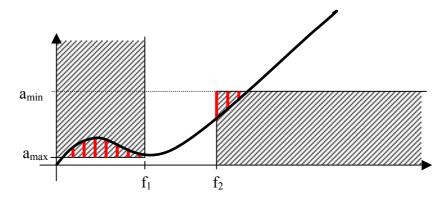

Figure. 2.4. RMS error for a low-pass filter: only differences in shaded areas are considered

An example of evaluation is indicated in the above Figure 2.4 for a low-pass filter. The requirements are denoted by the shaded rectangles, the transmission of the given circuit is denoted by the thick black line. The resultant RMS error is computed as the root mean square of the differences, marked as vertical red lines below respective above the computed characteristics of the given filter.

As follows from the above description, we want to minimize this RMS error. The wanted circuit is found, when this objective function is equal to zero.

Remark, that the requirements (and the differences) can be also weighted. It gives us for example a possibility to put some stress to some key frequencies (e.g.  $f_1$  and  $f_2$  in Figure 2.3), what can help the algorithm faster reach the optimum. We can also set a limit for the RMS error, which says that we do not require an optimal solution (with all requirements met - error equal to zero) but a solution with the RMS error below this limit. For example, a circuit with error below 1 dB can be sufficient for us. Such solution can be much easier to find than the optimal one (with RMS error equal to zero).

# 2.4. Circuit's Neighbourhood

As described in the previous chapter, in each evolution step, a solution (or configuration) is derived somehow from the previous solution. This can be also seen as selection of an element from the solution's neighborur solutions. In this paragraph we will discuss a neighbour circuit creation from the previous circuit by applying one of the "circuit" operation. Most of these operations are deducted from the graph representation of a circuit described above.

Let's define a circuit neighbourhood as a set of circuits created by applying of one of the below listed operations. An operation is applied only if the resultant circuit is consistent – it is connected, there is no vertex with more than four edges and every vertex has an appropriate circuit element associated (with the correct number of ports).

The operations are:

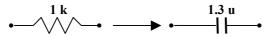

O1. A parameter of some circuit element is changed. (e.g. resistor's resistance is changed).

$\bullet \xrightarrow{1 \text{ k}} \bullet \xrightarrow{2.3 \text{ k}} \bullet$

Figure 2.5. A parameter of some element is changed

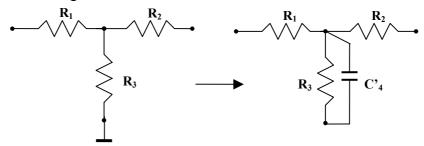

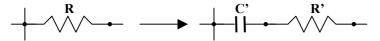

O2. A circuit element associated to a vertex or to an edge is replaced by another suitable one (with the same number of ports, e.g. a resistor is changed to a capacitor).

Figure 2.6. A circuit element is replaced by another one

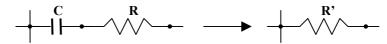

O3. An edge is added between two suitable vertices (with the number of connected edges below four, not i/o vertices). Elements of respective vertices are changed – the number of ports is increased by one. An arbitrary suitable circuit element (2-port) is associated to the created edge.

Figure 2.7. An edge is added between two vertices

O4. **An edge is removed.** Elements of appropriate vertices are changed – the number of ports is decreased by one. The graph has to remain connected.

Figure 2.8. An edge is removed

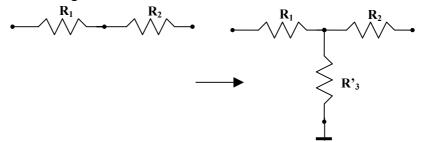

O5. A vertex (with two or more edges) is split up into two vertices and an edge is added between them. Suitable circuit elements are assigned with the created vertices and the created edge.

Figure 2.9. A vertex is split up to two vertices

O6. A single-edge vertex is created and connected with an edge to suitable vertex (with less then four connections, not i/o vertex). Suitable elements are assigned to the changed vertex and to the created edge and vertex.

Figure 2.10. A vertex is created and connected to a suitable vertex

O7. An arbitrary edge is split into two edges and a vertex is added between them. Suitable elements are assigned to the created edge and vertex.

Figure 2.11. An edge is split into two edges with an edge between

O8. A vertex with one edge (not i/o vertex) is removed. The appropriate edge is also removed. The element on the other side of the removed edge is changed.

Figure 2.12. A single-edge vertex is removed

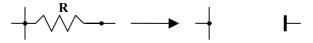

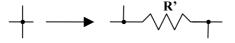

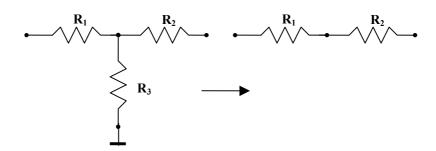

O9. A vertex with two edges is removed. The appropriate edges are joined into the one edge. Suitable element is assigned the created edge (e.g. an element from one of the removed edges is used).

Figure 2.13. A vertex with two edges is removed.

O10. Two suitable vertices connected with an edge are joined into the one vertex. The edge between the previous vertices is removed. Suitable elements are assigned to the created edge and vertex.

Figure 2.14. Two connected vertices are joined

There are also many other possibilities what operations to use, for example the above operations can be adopted not to violate planarity of the circuit (e.g. operation O3 can break the planarity if it remains defined as above). There can also be other circuit limitations introduced, e.g. for the maximum number of elements, elements of given type or physical feasibility of the resultant circuit.

Each circuit element, which can be used has a defined set of its parameters with minimal and maximal bounds and implicit values. When an edge or a vertex is created or changed, an appropriate element is selected randomly (or according to some heuristics). The element's parameters are selected from the log-normal distribution with the mean value equal to the parameter's implicit value. When a parameter is changed (the operation O1 in the above list), a new value is selected again from the log-normal distribution, but with mean value equal to the parameter's previous value.

Remark, that there are also operations for simplifying the graph (e.g. by removing an edge or a vertex). It gives us possibility to return (e.g. from some local-minima) in local search algorithm.

Also remark, that the neighbour of a circuit can be extremely large even if the parameters of all circuit elements will have finite domains (obtained by fixed accuracy of the parameters). Only for adding an edge we have approximately  $m^2$  possibilities how to select the vertices (*m* is number of vertices), exactly:

# $|\mathbf{V}'| \cdot (|\mathbf{V}'| - 1)$ Figure 2.15. Number of possibilities to add an edge

where V' is the set of the suitable vertices (all vertices except the vertices with assigned i/o element and vertices with four edges connected). Next, for such selection of suitable vertices, we have also many possibilities what element to select to the created edge and what values to assign to the parameters of the selected circuit element.

### 2.5. Initial Configuration

Till now, we have defined input requirements, a representation of an arbitrary microwave circuit and its evaluation. We have also described circuit's neighbour solutions. But for the design of an algorithm, there is still one thing missing. We have to define the initial configuration, the circuit which we will start from. But this task is rather easy, we can for example create a graph with directly connected input/output vertices. Some inner vertices can occur, as shown in Figure 2.16 for 3 input/output ports.

$$\mathbf{v}_{1} \quad \mathbf{v}_{4} \quad \mathbf{v}_{2} \qquad \text{Input/output vertices: } \mathbf{V}_{io} = \{v_{1}, v_{2}, v_{3}\}$$

$$\mathbf{BLO \ CIRCUIT \ 1 \ 2 \ 3}$$

$$\mathbf{ITEE \ 1 \ 2 \ 3}$$

$$\mathbf{Eisens \ 2 \ 16 \ Initial \ 2 \ next \ sinvit \ red \ the \ restruction is to set \ list$$

Figure 2.16. Initial 3-port circuit and the appropriate net-list

# 2.6. Algorithm

Now, we are ready to propose an algorithm for the evolutionary design of microwave circuits. This algorithm works with single member population and it is derived from the local search technique. An initial proposal of such algorithm is shown in the below Figure 2.17.

```

procedure EDMC-LS(max iters)

s <- initial circuit; //initial solution</pre>

err <- eval(s); //RMS error of the initial solution</pre>

//iterations counter

i <- 0;

while i<max iters end err>0 do

//operation selection

op <- select operation();</pre>

s' <- apply_operation(s,op); //operation application

//new RMS error

err' <- eval(s');</pre>

if acceptable(err,err') then //accept change

s <- s';

err <- err';

end;

i <- i + 1;

//increase iteration counter

end while

return s:

end EDMC-LS

```

Figure 2.17. Local search algorithm

The algorithm works in iterations. It starts from the initial solution, which is a simple circuit with only input/output ports connected (as described in section 2.5. and Figure 2.16).

In each iteration step, an operation is selected somehow and it is applied to the current solution. If the altered solution is acceptable (e.g. it is better then the current), it becomes the current solution for the next iteration. Otherwise, it is refused.

The iteration process stops when the requested solution (with RMS error equal to zero, or less then given limit) or the maximum number of iterations is reached. In case of the reach of the maximum number of iteration, the algorithm can

- return fail requested solution was not found

- return the best solution ever found the solution with the lowest evaluation (RMS error). Remark, that in case of random walk, simulated annealing or stochastic hill climbing, the best solution need not be the current solution from the last iteration. The algorithm can sometimes accept worse solution to the next iteration.

- restart the search from the beginning (or maybe from some previous memorized solution). This makes sense only when the above described algorithm is somehow randomized: The selection of an operation (and its operands edges, vertices, circuit elements, their parameters) and/or solution acceptance is not deterministic.

The above described algorithm is parameterized by two functions: The first one is the selection of an operation to be applied on a current circuit solution. The second one is the acceptance criterion for an altered circuit.

# 2.6.1. Operation Selection

For the operation selection criterion, we propose the operations to be selected randomly, but with the respect of their weights. This gives us a possibility to determine the frequency of use of each operation. So, for example, the modification of a single parameter or circuit element can be more frequent than an insertion of an edge. This way, we can also drive the speed of magnification of the circuit's complexity. These weights can also be changed during the search, e.g. according to the current solution, its complexity and evaluation or according to some statistics of successfulness of the previous operation and operands selections. After an operation is selected, there has to be also its operands selected, namely:

- appropriate vertices and/or edges, required for the operation (e.g. a suitable pair of vertices for adding an edge)

- appropriate circuit elements for new or altered edges and vertices (e.g. an element for a new edge and for the two altered vertices when there an edge should be added)

- parameters of the new or altered circuit elements

These operands can be selected also randomly, uniformly or with respecting some priorities from the set of suitable vertices, edges and circuit elements.

We already proposed (in the section 2.4) to select parameters of a circuit element from the log-normal distribution respecting the parameter bounds and its previous (in case of altering the parameter, see operation O1) or its implicit value (in case of new circuit element). The distribution will have the mean value equal to the previous or implicit value. When a value outside the bounds is selected, the appropriate maximum or minimum bound value is returned. The reason of choosing the log-normal distribution is based on the idea of selecting a value not too different from the previous or implicit value. For example, when there is a resistor with implicit resistance 50 ohms, we want the most of the new resistance values to be selected from the interval <0.5,5000> ohms – plus/minus two orders.

### 2.6.2. Acceptance Criterion

There were several types of acceptance criteria described in the first chapter of this thesis. We can accept **only better circuits**, introduce **random walk** technology (besides accepting only better circuits, we accept an arbitrary solution with some small probability), **simulated annealing** (probability of acceptance of worse solution depends on the difference, how much worse the solution is) and **stochastic hill climbing** (probability of acceptance of any solution depends on its quality according to the previous one). We propose to use either simulated annealing or stochastic hill climbing in the implementation because we need to escape a local minimum, e.g. when there is a long sequence of worse neighbour solution generated – to try select one of them. But we also do not want to select too bad neigbour.

We use only a simple schedule of the temperature in the simulated annealing techniques: the temperature is linearly decreasing from an initial temperature to some minimal (almost zero) temperature. After this minimum is reached, the temperature remains constant for the rest of the search.

### 2.7. Algorithm Improvements

Because the above described algorithm was unable to find a solution in reasonable time for many even simple toy instances, in the following paragraphs we will propose several improvements, developed for the better efficiency and stability of the algorithm.

### 2.7.1. Local (Parameter) Optimization

Because the selection of an operation and its operands can be rather expensive and because it will probably fail many times only just because the wrong parameters of the created or altered circuit elements are selected. We propose to try to change these parameters several times before the operation is totally rejected.

For example, when there is a need to decrease a single parameter of one element: Once this parameter (and appropriate operation which do this) is selected, we can improve the efficiency if the change of the parameter is tried several times. It can be also sometimes accepted during this, e.g. when the change of the parameter goes to the right direction (circuit's evaluation value decreases). This can be seen as a simple optimization of the selection of the new or altered elements' parameters. Improved algorithm is shown in Figure 2.18.

```

procedure EDMC-LSO(max iters, max tries)

s <- initial circuit; //initial solution</pre>

//RMS error of the initial solution

err <- eval(s);

i <- 0;

//iterations counter

while i<max iters and err>0 do

op <- select_operation(); //operation selection

s' <- apply_operation(s,op); //operation application</pre>

op <- select_operation();</pre>

err' <- eval(s');</pre>

//new RMS error

for t:=1 to max_tries do

if acceptable(err,err') then //accept change

s <- s'; err <- err';

end if

s' <- alter parameters(s,op); //modify solution</pre>

err' <- eval(s');</pre>

//new RMS error

end for

i <- i + 1;

//increase iteration counter

end while

return s:

end EDMC-LSO

```

Figure 2.18. Local search algorithm with local optimization

### 2.7.2. Backtracking

Because the algorithm can struggle in some local optimal solution, where all neighbour solutions are worse, there has to be a technique to get out of this point. There are two basic methods: The first one restarts the search process after a local optimum (or the maximum number of iteration) is reached. The second one tries to avoid staying in some local optimum point by randomization of the search (e.g. random walk techniques).

Empirical results has shown, that a use of only the second technique (simulated annealing and hill climbing was tested) can sometimes lead to a circuit which is very hard or almost unable to improve (e.g. the circuit is too complex).

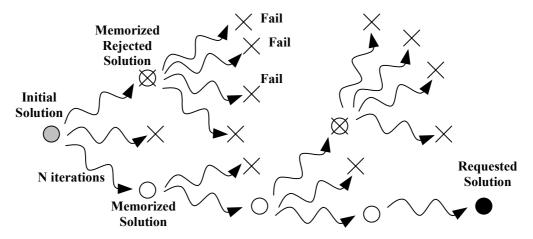

So, we proposed to use also the first method, but we do not restart from the beginning of the search. After a certain amount of iterations, the solution is memorized and compared to the previous memorized one. If the solution is not much better (e.g. the RMS error of the solution is not 10% or more lower than the RMS error of the previous solution), the algorithm jumps back to the previous memorized solution. Each such memorized solution has also included a counter of these back jumps to it. If this counter exceeds some value, the algorithm does not jump back to it, but to its memorized ancestor. In some sense, this approach mimics a backtracking search.

An example of such behaviour is shown in Figure 2.19. After each N iterations are applied, the solution is compared to the previous memorized one or initial when there is no previous memorized solution – called *choice point*, denoted by circle. When the solution is not much batter (e.g. evaluation of a solution is not less then the evaluation of the previous memorized (or initial) solution decreased by 10%) the solution is rejected (denoted by cross) and the search continues again from the previous memorized (or initial) solution. The amount of executions the search from memorized solution is limited to four in the below example. When

this number is reached the memorized solution is also rejected (denoted by crossed circle) and the search starts from the previous memorized one etc. Improved algorithm is shown in Figure 2.20.

Figure 2.19. Memorizing solutions, backtrack approach

| procedure EDMC-LSOB(max iters, max tries, max backs)                      |                                            |  |

|---------------------------------------------------------------------------|--------------------------------------------|--|

| s <- initial circuit; //initial solution                                  |                                            |  |

| <pre>err &lt;- eval(s); //RMS</pre>                                       | error of the initial solution              |  |

| b <- 0; back[b].s <- s;                                                   | //memorize initial solution                |  |

| <pre>back[b].err &lt;- err;</pre>                                         |                                            |  |

| <pre>back[b].backs &lt;- 0; //numb</pre>                                  | er of returns to the solution              |  |

| <pre>while b&gt;0 or backs[b]<max backs[b]<="" pre=""></max></pre>        | cks <b>do</b>                              |  |

| i <- 0;                                                                   | iterations counter                         |  |

| while i <max and="" er<="" iters="" th=""><th>r&gt;0 <b>do</b></th></max> | r>0 <b>do</b>                              |  |

| op <- select operation                                                    | on(); //operation selection                |  |

| s' <- apply operation                                                     | n(s,op); //operation application           |  |

| err' <- eval(s');                                                         | //new RMS error                            |  |

| <pre>for t:=1 to max_trie</pre>                                           | s <b>do</b>                                |  |

| <pre>if acceptable(er;</pre>                                              | r,err') <b>then</b> //accept change        |  |

| s <- s'; err                                                              | <- err';                                   |  |

| end if                                                                    |                                            |  |

|                                                                           | <pre>meters(s,op); //modify solution</pre> |  |

| err' <- eval(s')                                                          | ; //new RMS error                          |  |

| end for                                                                   |                                            |  |

| i <- i + 1;                                                               | <pre>//increase iteration counter</pre>    |  |

| end while                                                                 |                                            |  |

|                                                                           | ; //return solution if found               |  |

|                                                                           | then //new choice point                    |  |

| b <- b + 1;                                                               |                                            |  |

| <pre>back[b].s &lt;- s;</pre>                                             | //memorize solution                        |  |

| <pre>back[b].err &lt;- err;</pre>                                         |                                            |  |

| <pre>back[b].backs &lt;- 0;</pre>                                         |                                            |  |

| end else                                                                  | <pre>//back to previous choice point</pre> |  |

|                                                                           | <pre>//return to memorized solution</pre>  |  |

| <pre>err &lt;- back[b].err;</pre>                                         |                                            |  |

|                                                                           | k[b].backs + 1; //increase counter         |  |

| end if                                                                    |                                            |  |

(continues on the next page)

Figure 2.20. Local search with optimization and backtrack approach

# 2.7.3. RMS Error Estimation

According to the tests made on the above proposed algorithm (see chapter 4 for details), most time of the program's computation (at least 85%) was spend in the analysis of the circuit. Therefore, in this section we propose a technique, which will estimate the result of the suggested operation. The technique will use the knowledge acquired from the previous application of the appropriate operation. According to this estimation of improvement (or degradation) of the current solution a probability of direct rejection of the proposed operation will be computed.

```

procedure EDMC-LSOBE(max_iters, max_tries, max_backs)

s <- initial circuit; //initial solution</pre>

err <- eval(s); //RMS error of the initial solution</pre>

b <- 0; back[b].s <- s; //memorize initial solution</pre>

back[b].err <- err;</pre>

back[b].backs <- 0; //number of returns to the solution</pre>

stat <- {};</pre>

//statistics (empty or some default)

while b>0 or backs[b]<max_backs do</pre>

i <- 0;

//iterations counter

while i<max iters and err>0 do

op <- select operation();</pre>

//operation selection

prjc <- estimate_reject_prob(stat, op);//pr. rejection

if (random(0,1) > prjc) then //otherwise reject

s' <- apply_operation(s,op); //op. application</pre>

err' <- eval(s');

//new RMS error

update_stat(stat,op,err'-err); //update statist.

for t:=1 to max_tries do

if acceptable(err,err') then //accept change

s <- s'; err <- err';

end if

s' <- alter parameters(s,op); //modify sol.</pre>

err' <- eval(s');</pre>

//new RMS error

update stat(stat,op,err'-err);

end for

end if

i <- i + 1;

//increase iteration counter

end while

if (err=0) then return s; //return solution if found

if (err<br/>back[b].err*0.9) then //new choice point

b <- b + 1;

back[b].s <- s;</pre>

//memorize solution

back[b].err <- err;</pre>

back[b].backs <- 0;</pre>

end else

//back to previous choice point

```

*(continues on the next page)*

```

s <- back[b].s; //return to memorized solution

err <- back[b].err;

back[b].backs <- back[b].backs + 1; //increase counter

end if

while b>0 and back[b].backs>max_backs do

b <- b - 1; //maximum returns is reached

s <- back[b].s; //return to previous memorized sol.

err <- back[b].err;

back[b].backs <- back[b].backs + 1; //increase counter

end while

end while

return fail; //or best solution ever found

end EDMC-LSOBE

```

Figure 2.21. Local search with optimization, backtrack and RMS estimation

Adopted algorithm is shown in Figure 2.21. There is a new entity introduced in the algorithm: a statistics of "successfulness" of the applied operations so far. This statistics is updated after each evaluation of a solution (circuit) and it takes the difference of latest and previous evaluation and the applied operation (or some classification of this operation) into account. According to this statistics, after an operation is selected, the probability of direct rejection of the operation is computed. If the probability is then met the operation is refused and the algorithm continue with the another operation selection in the next iteration. Otherwise, the algorithm continues as before – with applying the operation, evaluation of the new circuit, computing whether the change is acceptable and so on. We assume that the probability of rejection (because it is only some estimation) will never be equal to one, e.g. we can limit it to 0.9.

Because we cannot compute the rejection probability only from the operation (it is too inaccurate) or from the operation and from all the operands (there will be very probably no exactly the same operation selected before) we propose a simple classification of an operation and operands. The rejection probability is then computed from the previous achieved differences of operations from the same class. The idea is, to describe each operation with a short string (descriptor). This also helps us to hash the operation classes in accordance with this string. This descriptor is also proposed to be easily readable.

Circuit elements are classified by its name in net-list (e.g. RES, IND, MISTR, ITEE). In the case that the element is assigned to a vertex, there is also a prefix '1', '2', '3' or '4' added according the number of edges connected to the vertex. Otherwise, when the element is assigned to an edge, there is also a prefix 'p', 's' or 'c' included in the classification, according to the edge's location in the circuit:

- **s:** If this edge is removed, the graph become disconnected (graph is divided into the two parts with no edge between them) and both parts contain at least one input/output port.

- **p:** If this edge is removed, the graph become disconnected, but all input/output ports are located in only one part. (See Figure 2.22.)

- **c:** If this edge is removed, the graph remain connected. The edge creates a circle in the graph.

2.22. Circuit element classification

The classification of an operation consists of above described classifications of used elements (created, removed and modified) in the scheme expressing the behaviour of the operation. If there is an edge or a vertex with no (zero) element assigned, the edge or vertex is classified with the name "z" (zero element assignment). In case of the operation O1 (which changes only a single parameter of a selected element), the element classification is followed by the change direction (+ for increasing the parameter, - for decreasing). This direction mark can be repeated several times according to the extent of a change – one mark for a difference less then 25% (of previous value), two marks for a difference less then 50%, three if less then 75% and four otherwise. Some examples are shown in Figure 2.23.

| 01:  | pRES R OI                         | ne parameter is changed       |

|------|-----------------------------------|-------------------------------|

|      | sMISTR L+++                       |                               |

|      | pMISTR W++                        |                               |

| 02 : | SMISTR -> SRES OI                 | ne circuit element is chanded |

|      | 1SHORT -> 10PEN                   |                               |

| 03:  | 1SHORT 3ITEE -> z-cRES-4ICROS     | an edge is added              |

| 04:  | 3ITEE-sRES-z -> z 10PEN           | an edge is removed            |

| 05:  | 4ICROS -> 3ITEE-cMISTR-3ITEE      | a node is split to two nodes  |

|      | 4ICROS -> z-cMISTR-4ICROS         |                               |

|      | <b>3ITEE -&gt; 3ITEE-sMISTR-z</b> |                               |

| 06:  | z -> 3ITEE-pRES-1SHORT            | a vertex w. an edge is added  |

|      | 3ITEE -> 4ICROS-pMISTR-10PEN      |                               |

| 07:  | sRES -> sRES-z-sCAP               | an edge is split to two edg.  |

| 08:  | 4ICROS-pMISTR-10PEN -> 3ITEE      | a vertex w. 1 edge is remov.  |

| 09:  | pRES-z-pCAP -> pRES               | 2 edges are joined into 1     |

|      | sRES-z-sRES -> sRES               | a vertex w. 2 edges is rem.   |

| 010: | <b>3ITEE-sRES-z -&gt; 3ITEE</b>   | 2 connected vertices are      |

|      | 3ITEE-SRES-3ITEE -> 4ICROSS       | joined into one               |

Figure 2.23. Examples of operation classes (descriptors)

So, the probability of rejection of a selected operation (with also selected operands) is counted according to the successfulness (differences err'-err) of the previous evaluated operations of the same class (operations with the same descriptor). We can for example use the mean value of the previous computed differences for estimation of the new difference. The probability of acceptance can be counted from such estimated differences according to the formula used in simulated annealing (Figure 1.8.) or stochastic hill climbing (Figure 1.10), respective one minus probability of acceptance, which is computed there. We can also use variances of these differences for estimation of the variance of the

estimated difference. If we are unable to compute the rejection probability because the set of the similar previous evaluated operations is not large enough, we can set this probability to zero.

This approach can be also adopted to be used as guidance for the operation selection.

# 2.8. Conclusion

We have proposed a promising algorithm based on single member evolution and local search techniques which is able to solve many interesting assignments. We also proposed several improvements to this algorithm.

In the following chapter, we will discuss some implementation aspects of this algorithm and in the fourth chapter we will present some results achieved with this algorithm.

# 3. Implementation Issues

In this chapter, we will discuss some implementation issues of the above proposed and described algorithm. The algorithm is written in JAVA (JSDK 1.4.1). Complete documentation of all implemented classes is generated in HTML format (via JavaDoc) and included on the CD which is a part of this thesis.

The whole implementation is divided into several packages (see Figure 3.1.). We will discuss these packages in the following paragraphs.

| Description                                      |

|--------------------------------------------------|

| Circuit elements.                                |

| Representation of a circuit (graph)              |

| Operation over circuits                          |

| Input (frequency) requirements                   |

| Analysis – connection to program MIDE            |

| Circuit design – implementation of the algorithm |

| Supporting classes                               |

|                                                  |

Figure 3.1. Packages

# 3.1. Circuit Elements

Each circuit element, which can be used in the design, has appropriate element in the MIDE's net-list and also appropriate class implemented. Such class has to be extended from the abstract class *edmc.elements.AbstractElement*. It has to have several methods implemented:

| Method                | Description                                                                                        |

|-----------------------|----------------------------------------------------------------------------------------------------|

| constructor           | Creates an element, assign values to all parameters.                                               |

| getNrGates()          | Returns number of ports of the element (e.g. 2 for resistor)                                       |

| getNrParams()         | Returns number of parameters of the element (e.g. 1 for resistor – its resistance)                 |

| getParameterBounds(i) | Returns i-th parameter's bounds                                                                    |

| getName()             | Returns name of the element in MIDE                                                                |

| getParameter(i)       | Returns value of the i-th parameter                                                                |

| setParameter(i,val)   | Sets value of the i-th parameter                                                                   |

| toString(int[] nodes) | Return net-list representation of the element (as a string)                                        |

| getWidthParam(int i)  | For micro-stripes: returns the number of the parameter<br>which represents width for the i-th port |

|                       | (or -1 otherwise, e.g. if there is no width)                                                       |

Figure 3.2. Element's API

Probably the most interesting part of the API is the method *toString(int[])*. It has one parameter – the array of numbers – which are assigned to the appropriate ports of the element. Result is a string, appropriate line of the net-list representation. An example implementation of this method for resistor is shown in Figure 3.3. (attribute *iR* represents the resistance parameter)

*Figure 3.3. An example implementation of toString(int[]) for resistor*

There is also an API to propagation micro-stripe's width between connected elements, this can be made via method *getWidthParam(int)*. But, because there is a bug in the analysis tool, which is used in this work, micro-stripe connection elements (e.g. MKR4, MTE4) cannot be used anyway (MIDE always fails with some error).

All access to the element (e.g all changes of parameters) is made through this API. So, a new element can be easily added to the system, just appropriate element's class has to be written. For more information, see appendix B, section B.1.

### **3.2.** Circuit Representation

A circuit is represented by a graph, implemented with classes in *edmc.circuits* package, namely:

| Class                            | Description                                     |

|----------------------------------|-------------------------------------------------|

| Vertex                           | Representation of a vertex.                     |

| Edge                             | Representation of an edge                       |

| Graph                            | Representation of graph, API for basic graph    |

|                                  | operations (e.g. add or remove a vertex or an   |

|                                  | edge) included                                  |

| Circuit                          | Representation of a circuit: graph plus circuit |

|                                  | operation (e.g. printing a net-list)            |

| SerialNumberFactory              | Generator of unique numbers for vertices and    |

|                                  | edges (e.g. to be used in net-list)             |

| Figure 2.2 Dackage adme sinewite |                                                 |

Figure 3.3. Package edmc.circuits

Basically a graph is represented by vertices and edges (connections between vertices). Besides the traditional graph-based functionality (e.g. to enumerate connected vertices to a given vertex), there is also information and API for assignment of a circuit element to a vertex or an edge and to maintenance unique serial numbers for vertices (one per vertex, e.g. for comparison of two vertices) and for edges (two per edge, one for each end – to be used in the net-list representation). Class *Graph* provides basic graph functionality, for example for counting and enumerating all edges and vertices, to add or remove an edge or a vertex, to check whether a vertex or an edge can be removed (graph has to remain

connected) and last but not least for cloning a graph (used e.g. for memorizing previous configuration). Class *Circuit* provides the circuit-based functionality, it creates an initial circuit, it determines whether a vertex is an input/output port or not, it collects information about available circuit elements, it prints net-list representation and enumerates edge and vertex classification (e.g. sRES string). There is also API for cloning circuits. The following Figure 3.4 shows an example of creating a circuit. Resultant net-list representation is presented in Figure 3.5.

```

Circuit c = new Circuit(2, "test"); // 2 i/o ports, name is test

//drop initial edge between i/o ports

c.getGraph().dropEdge(c.getIO(0),c.getIO(1));

Vertex v1 = c.getGraph().createVertex(); // new vertices

Vertex v2 = c.getGraph().createVertex();

Vertex v3 = c.getGraph().createVertex();

Edge ei1 = c.getGraph().createEdge(c.getIO(0),v1); //new edges

Edge e1o = c.getGraph().createEdge(v1, c.getIO(1));

Edge e12 = c.getGraph().createEdge(v1,v2);

Edge e13 = c.getGraph().createEdge(v1,v3);

v1.setElement(new ICROS()); //assign elements to vertices

v2.setElement(new OPEN());

v3.setElement(new SHORT());

//assign element to edges - set appropriate parameters

ei1.setElement(new RES());ei1.getElement().setParameter(0,75.0);

e1o.setElement(new CAP());e1o.getElement().setParameter(0,1e-6);

e12.setElement(new IND());e12.getElement().setParameter(0,2.3e-9);

e13.setElement(new RES()); e13.getElement().setParameter(0,1e3);

//print resultant net-list representation

c.printNetlist(System.out);

```

Figure 3.4. A circuit example

BLO test 1 4 RES 1 2 R=75 ohm CAP 3 4 C=1 miF ICROS 2 5 3 7 IND 5 6 L=2.3 nH RES 7 8 R=1000 ohm OPEN 6 SHORT 8 END

Figure 3.5. A circuit example – resultant net-list

### 3.3. Operations

Available circuit operation are located in the package *edmc.operations*, each circuit operation has to be extended from abstract class *edmc.operations*. *CircuitOperation*. There has to be following four methods implemented:

| Method                      | Description                                                          |  |

|-----------------------------|----------------------------------------------------------------------|--|

| boolean                     | Selects operation's operands, applies the operation to the current   |  |

| process()                   | circuit and returns true. If there are no suitable operands (e.g. no |  |

|                             | edge can be removed) it returns false (operation was not applied).   |  |

| boolean                     | Local optimization: it changes parameters affected by previous call  |  |

| redo()                      | of method process (or redo, when the changes are accepted). (redo    |  |

|                             | can be called several times)                                         |  |

| good()                      | Called when changes made by process or redo are accepted.            |  |

| toString()                  | Returns operation's classification (descriptor)                      |  |

| Figure 3.6. Operation's API |                                                                      |  |

So, in each iteration step, the current circuit is memorized first. An operation is selected and the appropriate method *process* is called then. If it returns false, nothing was changed and the algorithm returns to the selection of an operation. Otherwise, the changed circuit is evaluated and if the local optimization is used (as described in section 2.7.1) the method *redo* is called several times (to optimize parameters changed by method *process*). If the changed circuit is accepted, method *good* is called (can be called after *process* method and each *redo*). This affects the mean values of the distribution used the selection of parameters' values (previous accepted values are used). Last accepted circuit is used for the next iteration.

# 3.4. Frequency Requirements

Classes for representation of the input requirements (on the given frequecy) are located in the package *edmc.frequency*. These classes also provide computation of the resultant RMS error from the values computed in analysis. There are classes:

| Class            | Description                                                                                                                            |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------|